# **Epiphany Architecture Reference**

# **Table of Contents**

| 1          | Introduction                         |    |

|------------|--------------------------------------|----|

| 2          | Programming Model                    |    |

| 2.1        | Programming Model Introduction       |    |

| 2.2        | Parallel Programming Example         | 14 |

| 3          | Software Development Environment     |    |

| 4          | Memory Architecture                  |    |

| 4.1        | Memory Address Map                   | 17 |

| 4.2        | Memory Order Model                   | 19 |

| 4.3        | Endianness                           | 20 |

| 4.4        | Load/Store Alignment Restrictions    | 21 |

| 4.5        | Program-Fetch Alignment Restrictions | 21 |

| 5          | eMesh Network-On-Chip                | 22 |

| 5.1        | Network Topology                     |    |

| 5.2        | Routing Protocol                     |    |

| 5.3        | Read Transactions                    | 25 |

| 5.4        | Direct Inter-Core Communication      |    |

| 5.5        | Arbitration Scheme                   | 27 |

| 5.6        | Data Sizes and Alignment             | 27 |

| 5.7        | Multicast Routing                    |    |

| 5.8        | Detour Routing Support               |    |

| 6          | Processor Node Subsystem             |    |

| 6.1        | Processor Node Overview              |    |

| 6.2        | Mesh-Node Crossbar Switch            |    |

| 6.3        | Mesh-Node Arbitration                |    |

| 7          | eCore CPU                            |    |

| 7.1        | Overview                             |    |

| 7.2        | Data Types                           |    |

| 7.3        | Local Memory Map                     |    |

| 7.4        | General Purpose Registers            |    |

| 7.5        | Status Flags                         |    |

| 7.6        | The Epiphany Instruction Set         |    |

| 7.7        | Pipeline Description                 |    |

| 7.8        | Interrupt Controller                 |    |

| 7.8<br>7.8 |                                      |    |

| 7.8<br>7.8 |                                      |    |

| 7.8        | •                                    |    |

| 7.9        | Hardware Loops (LABS)                | 67 |

| 7.10       | Debug Unit                           |    |

| 8                                            | Direct Memory Access (DMA)         | 69    |

|----------------------------------------------|------------------------------------|-------|

| 8.1                                          | Overview                           | 69    |

| 8.2                                          | DMA Descriptors                    | 71    |

| 8.3                                          | DMA Channel Arbitration            | 71    |

| 8.4                                          | DMA Usage Restrictions             | 71    |

| 8.5                                          | DMA Transfer Examples              | 72    |

| 9                                            | Event Timers                       | 73    |

| 10                                           | Memory Protection Unit (LABS)      | 74    |

| Арр                                          | endix A: Instruction Set Reference | 75    |

|                                              | )                                  |       |

| ANI                                          | )                                  | 77    |

| ASR                                          |                                    | 78    |

| B <c< td=""><td>OND&gt;</td><td>79</td></c<> | OND>                               | 79    |

| BL.                                          |                                    | 80    |

| BKP                                          | Т                                  | 82    |

| EOR                                          |                                    | 83    |

| FAB                                          | S                                  | 84    |

| FAD                                          | D                                  | 85    |

| FIX.                                         |                                    | 86    |

| FLO                                          | AT                                 | 87    |

| FMA                                          | ADD                                | 88    |

| FMU                                          | 几                                  | 88    |

| FMS                                          | UB                                 | 90    |

| FSU                                          | В                                  | 91    |

| GID                                          |                                    | 92    |

| GIE                                          |                                    | 93    |

| IAD                                          | D                                  | 94    |

| IMA                                          | DD                                 | 95    |

| IMS                                          | UB                                 | 96    |

| IMU                                          | L                                  | 97    |

| ISUI                                         | 3                                  | 98    |

| IDLI                                         | Ε                                  | 99    |

| JAL                                          | R                                  | . 100 |

| JR                                           |                                    | . 101 |

| LDR                                          | (DISPLACEMENT)                     | . 102 |

| LDR                                          | L (INDEX)                          | . 103 |

| LDR                                          | (POSTMODIFY)                       | . 104 |

| LDR                                          | (DISPLACEMENT-POSTMODIFY)          | . 105 |

| LSL                                          |                                    | . 106 |

| LSR                                          |                                    | . 107 |

| MB                                           | KPT (LABS)                         | . 108 |

|                                    | 100 |

|------------------------------------|-----|

| MOV <cond></cond>                  |     |

| MOV (IMMEDIATE)                    |     |

| MOVT (IMMEDIATE)                   |     |

| MOVFS                              |     |

| MOVTS                              |     |

| NOP                                |     |

| ORR                                |     |

| RTI                                |     |

| RTS (alias instruction)            |     |

| SUB                                |     |

| STR (DISPLACEMENT)                 |     |

| STR (INDEX)                        |     |

| STR (POSTMODIFY)                   |     |

| STR (DISPLACEMENT-POSTMODIFY)      |     |

| SYNC (LABS)                        |     |

| TRAP                               |     |

| TESTSET                            |     |

| WAND (LABS)                        |     |

| Appendix B: Register Set Reference |     |

| Register Summary                   |     |

| CMESHROUTE (G4-LABS)               |     |

| COREID                             |     |

| CONFIG                             |     |

| CTIMER0                            |     |

| CTIMER1                            |     |

| DMAxAUTO0 (LABS)                   |     |

| DMAxAUTO1 (LABS)                   |     |

| DMAxCONFIG                         |     |

| DMAxCOUNT                          |     |

| DMAxDSTADDR                        |     |

| DMAXDSTADDR                        |     |

| DMAXSRCADDR                        |     |

| DMAXSTATUS                         |     |

| DEBUGCMD                           |     |

| DEBUGSTATUS                        |     |

|                                    |     |

| FSTATUS (LABS)                     |     |

| ILAT                               |     |

| ILATST                             |     |

| ILATCL                             |     |

| IMASK                              |     |

| IRET                               |     |

| IPEND                              |     |

| Appendix F: Copyright Information             |  |

|-----------------------------------------------|--|

| Appendix E: Architecture Manual Changes       |  |

| Appendix D: Architecture Evolutionary Changes |  |

| Appendix C: Instruction Set Decode            |  |

| XMESHROUTE (G4-LABS)                          |  |

| STATUS                                        |  |

| RESETCORE (LABS)                              |  |

| RMESHROUTE (G4-LABS)                          |  |

| PC                                            |  |

| MULTICAST (LABS)                              |  |

| MESHCONFIG (LABS)                             |  |

| MEMSTATUS (LABS)                              |  |

| MEMPROTECT (LABS)                             |  |

| LS (LABS)                                     |  |

| LE (LABS)                                     |  |

| LC (LABS)                                     |  |

# List of Figures

| FIGURE 1: AN IMPLEMENTATION OF THE EPIPHANY ARCHITECTURE |    |

|----------------------------------------------------------|----|

| FIGURE 2: EMESH™ NETWORK-ON-CHIP OVERVIEW                |    |

| FIGURE 3: MATRIX MULTIPLICATION DATA FLOW                | 15 |

| FIGURE 4: EPIPHANY SOFTWARE DEVELOPMENT STACK            | 16 |

| FIGURE 5: EPIPHANY GLOBAL ADDRESS MAP                    | 17 |

| FIGURE 6: EPIPHANY SHARED MEMORY MAP                     |    |

| FIGURE 7: EMESH™ NETWORK TOPOLOGY                        | 23 |

| FIGURE 8: EMESH™ ROUTING EXAMPLE                         |    |

| FIGURE 9: POINTER MANIPULATION EXAMPLE                   | 27 |

| FIGURE 10: PROCESSOR NODE OVERVIEW                       | 29 |

| FIGURE 11: PROGRAM MEMORY LAYOUT OPTIMIZED FOR SIZE      | 32 |

| FIGURE 12: PROGRAM MEMORY LAYOUT OPTIMIZED FOR SPEED     | 32 |

| FIGURE 13: ECORE CPU OVERVIEW                            |    |

| FIGURE 14: PIPELINE GRAPHICAL VIEW                       | 58 |

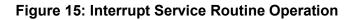

| FIGURE 15: INTERRUPT SERVICE ROUTINE OPERATION           | 63 |

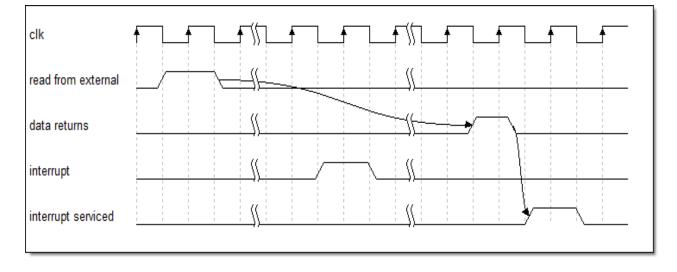

| FIGURE 16: INTERRUPT LATENCY DEPENDENCY ON EXTERNAL READ | 66 |

# List of Tables

| TABLE 1: MEMORY TRANSACTION ORDERING RULE                | 20  |

|----------------------------------------------------------|-----|

| TABLE 2: LOAD AND STORE MEMORY-ALIGNMENT RESTRICTIONS    | 21  |

| TABLE 3: ROUTING PROTOCOL SUMMARY                        | 25  |

| TABLE 4: PROCESSOR NODE ACCESS PRIORITIES                | 33  |

| TABLE 5: IEEE SINGLE-PRECISION FLOATING-POINT DATA TYPES | 38  |

| TABLE 6: ECORE LOCAL MEMORY MAP SUMMARY                  | 40  |

| TABLE 7: GENERAL-PURPOSE REGISTERS                       | 41  |

| TABLE 8: CONDITION CODES                                 | 47  |

| TABLE 9: INSTRUCTION SET SYNTAX                          | 50  |

| TABLE 10: BRANCHING INSTRUCTIONS                         | 51  |

| TABLE 11: LOAD/STORE INSTRUCTIONS                        | 52  |

| TABLE 12: INTEGER INSTRUCTIONS                           | 53  |

| TABLE 13: FLOATING-POINT INSTRUCTIONS                    | 54  |

| TABLE 14: SECONDARY INTEGER INSTRUCTIONS                 | 55  |

| TABLE 15: REGISTER MOVE INSTRUCTIONS                     | 55  |

| TABLE 16: PROGRAM FLOW INSTRUCTIONS                      |     |

| TABLE 17: PIPELINE STAGE DESCRIPTION                     |     |

| TABLE 18: PARALLEL SCHEDULING RULES                      |     |

| TABLE 19: IALU INSTRUCTION SEQUENCES                     |     |

| TABLE 20: FPU INSTRUCTION SEQUENCES                      |     |

| TABLE 21: LOAD INSTRUCTION SEQUENCES                     |     |

| TABLE 22: STALLS INDEPENDENT OF INSTRUCTION SEQUENCE     |     |

| TABLE 22: BRANCH PENALTIES                               |     |

| TABLE 24: INTERRUPT SUPPORT SUMMARY                      |     |

| TABLE 25: DMA TRANSFER TYPES                             |     |

| TABLE 26: DMA DESCRIPTORS                                |     |

| TABLE 27: ECORE REGISTERS                                |     |

| TABLE 27: LOOKE REGISTERS                                |     |

| TABLE 29: PROCESSOR CONTROL REGISTERS                    | -   |

| TABLE 29: TROCESSOR CONTROL REGISTERS                    |     |

| TABLE 30. DIVIA REGISTERS                                |     |

| TABLE 31: MESH NODE CONTROL REGISTERS                    | -   |

| TABLE 32: CIVIL STROOTE REGISTER                         |     |

| TABLE 33: CONFIG REGISTER                                |     |

| TABLE 34. CONFIG REGISTER                                |     |

| TABLE 35: CTIMERO REGISTER                               |     |

| TABLE 30. CTIMIERT REGISTER                              |     |

| TABLE 37: DIVIAXAUTOU REGISTER                           |     |

| TABLE 38: DIVIAXAUTOU REGISTER                           |     |

| TABLE 39: DMACONFIG REGISTER                             |     |

| TABLE 40: DMACOONT REGISTER                              |     |

| TABLE 41: DIVIADSTADDR REGISTER                          |     |

|                                                          |     |

| TABLE 43: DMASTATUS REGISTER                             |     |

| TABLE 44: DMASTRIDEREGISTER                              |     |

| TABLE 45: DEBUGCMD REGISTER                              |     |

| TABLE 46: DEBUGSTATUS REGISTER                           |     |

| TABLE 47: FSTATUS STATUS REGISTER                        |     |

| TABLE 48: ILAT REGISTER                                  |     |

| TABLE 49: ILATST REGISTER ALIAS                          |     |

| TABLE 50: ILATCL REGISTER ALIAS                          |     |

| TABLE 51: IMASK REGISTER                                 | 144 |

| TABLE 52: IRET REGISTER                     | 144 |

|---------------------------------------------|-----|

| TABLE 53: IPEND REGISTER                    | 144 |

| TABLE 54: LC REGISTER                       | 145 |

| TABLE 55: LE REGISTER                       | 145 |

| TABLE 56: LS REGISTER                       | 145 |

| TABLE 57: MEMPROTECT REGISTER               | 146 |

| TABLE 58: MEMSTATUS REGISTER                | 147 |

| TABLE 59: MESH CONFIGURATION REGISTER       | 148 |

| TABLE 60: MULTICAST REGISTER                | 149 |

| TABLE 61: PC REGISTER                       | 149 |

| TABLE 62: RESETCORE REGISTER                | 151 |

| TABLE 63: STATUS REGISTER                   | 151 |

| TABLE 64: XMESHROUTE REGISTER               | 153 |

| TABLE 65: OPCODE FIELD SUMMARY              |     |

| TABLE 66: EPIPHANY INSTRUCTION DECODE TABLE | 155 |

| TABLE 67: EPIPHANY ARCHITECTURE CHANGES     | 156 |

| TABLE 68: REFERENCE CHANGE LOG              | 157 |

# Preface

This document describes Adapteva's Epiphany<sup>TM</sup> architecture. The document is written for system programmers with a fundamental understanding of processor architectures and experience with C programming.

# **Related Documents**

- <u>Epiphany SDK Reference</u>: The development tools and run-time library for the Epiphany architecture.

- <u>Epiphany E16G301 Datasheet</u>: Datasheet for 16-core System-on-Chip implementation of the Epiphany architecture.

### "LABS" Features

Features labeled with the "LABS" label should be considered experimental.

# 1 Introduction

The Epiphany architecture defines a multicore, scalable, shared-memory, parallel computing fabric. It consists of a 2D array of compute nodes connected by a low-latency mesh network-onchip. Figure 1 shows an implementation of the architecture, highlighting the key components:

- A superscalar, floating-point RISC CPU in each mesh node that can execute two floating point operations and a 64-bit memory load operation on every clock cycle.

- Local memory in each mesh node that provides 32 Bytes/cycle of sustained bandwidth and is part of a distributed, shared memory system.

- Multicore communication infrastructure in each node that includes a network interface, a multi-channel DMA engine, multicore address decoder, and network-monitor.

- A 2D mesh network that supports on-chip node-to-node communication latencies in nanoseconds, with zero startup overhead.

#### Figure 1: An Implementation of the Epiphany Architecture

The Epiphany architecture was designed for good performance across a broad range of applications, but really excels at applications with high spatial and temporal locality of data and

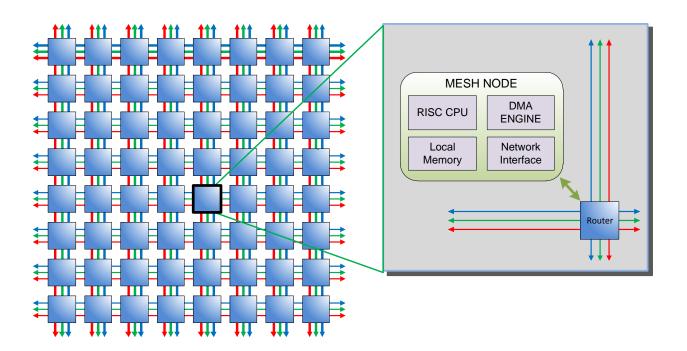

code. Examples of such application domains include: image processing, communication, sensor signal processing, encryption, and compression. High speed inter-processor communication is supported by the Epiphany architecture's 2D eMesh<sup>TM</sup> Network-On-Chip (NOC), shown in Figure 2, which connects the on-chip processor nodes. The mesh network efficiently handles traffic patterns in high-throughput real-time applications. The network takes advantage of spatial locality and an abundance of short point-to-point on-chip wires to send complete transactions— consisting of source address, destination address, and data—in a single clock cycle. Each routing link can transfer up to 8 bytes of data on every clock cycle, allowing 64 bytes of data to flow through every routing node on every clock cycle, supporting an effective bandwidth of 64 GB/sec at a mesh operating frequency of 1GHz.

Figure 2: eMesh<sup>™</sup> Network-On-Chip Overview

The memory map of the Epiphany architecture is flat and unprotected. Every mesh node has direct access to the complete memory system, without limitation. The architecture employs a flat 32-bit memory map and supports up to 4096 individual mesh nodes.

The shared-memory architecture and low-latency, on-chip mesh network allows multicore programs to pass messages from a few bytes to kilobytes with very little overhead. The high bandwidth and low latency of the eMesh<sup>™</sup> NOC means the Epiphany can support parallel programming at a large kernel as well as fine-grained level in which small tasks can be executed in parallel. The support of many different levels of parallelism within the Epiphany architecture is a true breakthrough that will make parallel programming much easier and effective by significantly reducing inter-task communication bottlenecks.

The key benefits of the Epiphany architecture are:

- **Ease of Use:** A multicore architecture that is ANSI-C/C++ programmable. This makes the architecture accessible to every programmer, regardless of his or her level of expertise.

- Effectiveness: The general-purpose instruction, superscalar instruction issue, and large unrestricted register file ensures that the application code written in ANSI-C can approach the peak theoretical performance of the Epiphany architecture.

- Low Power: Aggressive microarchitecture optimizations, streamlined feature sets, and extensive clock gating enables up to 70 GFLOP/Watt processing efficiency at 28nm.

- **Scalability:** The architecture can scale to thousands of cores on a single chip and millions of cores within a larger system. This provides the basis for future performance gains from increased parallelism.

# 2 Programming Model

# 2.1 Programming Model Introduction

The Epiphany architecture is programming-model neutral and compatible with most popular parallel-programming methods, including Single Instruction Multiple Data (SIMD), Single Program Multiple Data (SPMD), Host-Slave programming, Multiple Instruction Multiple Data (MIMD), static and dynamic dataflow, systolic array, shared-memory multithreading, message-passing, and communicating sequential processes (CSP). Adapteva anticipates that with time, the ecosystem around the Epiphany multicore architecture will grow to include many of these methods.

The key hardware features in the Epiphany architecture that enables effective support for parallel programming methods are:

- General-purpose processors that support ANSI C/C++ task level programming at each node. Shared-memory map that minimizes the overhead of creating task interfaces.

- Distributed-routing technology that decouples tasks from

- Inter-core message-passing with zero startup cost.

- Built-in hardware support for efficient multicore data-sharing.

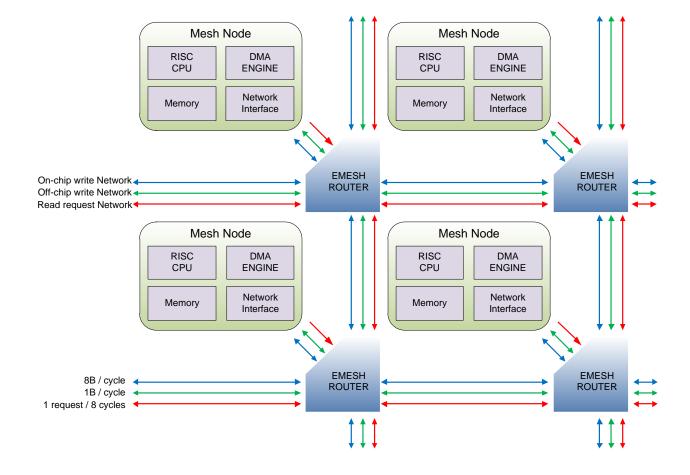

### 2.2 Parallel Programming Example

The following example shows how multiple Epiphany mesh nodes can be combined to improve the overall throughput of a computation. For simplicity, we have chosen matrix multiplication, but the concepts also apply to more complicated programs. Matrix multiplication can be represented by the following formula:

$$C_{ij} = \sum_{k=0}^{N-1} (A_{ik} B_{kj})$$

Where A and B are the input matrices, C is the result, and i and j represent the row-column coordinate of the matrix elements.

A naïve (but correct) implementation of the matrix multiplication running on a single core is given below:

The code above can be written in standard C/C++ and compiled to run on a single core, with matrices A, B, and C placed in the core's local memory. In this simple programming example, there is no difference between the Epiphany architecture and any other single threaded processor platform.

To speed up this calculation using several mesh nodes simultaneously, we first need to distribute the A, B, C matrices over P tasks. Due to the matrix nature of the architecture, the natural way to distribute large matrices is by cutting them into smaller blocks, sometimes referred to as "blocked by row and column". We then construct a SPMD program that runs on each of the mesh nodes.

Figure 3 shows how the matrix multiplication can be divided into 16 sub-tasks and mapped onto 16 mesh nodes. Data sharing between the sub tasks can be done by passing data between the cores using a message passing API provided in the Epiphany SDK or by explicitly writing to global shared memory.

Figure 3: Matrix Multiplication Data Flow

The parallel matrix multiplication completes in  $\sqrt{P}$  steps, (where P is the number of processors) with each matrix multiplication task operating on data sets that are of size  $\sqrt{P} \times \sqrt{P}$ . At each step of the process, contributions to the local C matrix accumulate in each task, after which the local A matrix moves down and the local B matrix moves to the right. The entire example can be completed using standard ANSI programming constructs. Epiphany run-time functions are provided to simplify multicore programming, but their use is not mandatory. The architecture allows programmers to innovate at all levels. For more information on the inter-processor communication API, please refer to the *Epiphany SDK Reference Manual*.

Given the algorithm above, a 16-core Epiphany implementation operating at 1GHz can complete a 128x128 matrix multiply in 2ms while achieving 90% of the theoretical peak performance. The matrix multiplication algorithm in this example scales to thousands of cores and demonstrates how the Epiphany architecture's performance scales linearly with the number of cores in the system when proper data distribution and programming models are used.

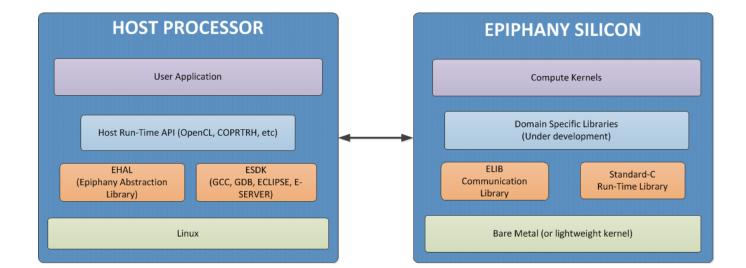

# 3 Software Development Environment

The Epiphany multicore architecture supports popular open-source ANSI C/C++ software development flows, using GNU GCC and GDB. The highly optimized GCC compiler enables acceptable real-time performance from pure ANSI-C/C++ applications without having to write assembly code for the vast majority of applications. The Epiphany SDK includes:

- ANSI-C/C++ GCC compiler

- OpenCL SDK

- Multicore GDB debugger

- Eclipse based multicore IDE

- Runtime library

- Fast functional single core simulator

Figure 4 shows the complete software stack of the Epiphany software development environment.

#### Figure 4: Epiphany Software Development Stack

# 4 Memory Architecture

### 4.1 Memory Address Map

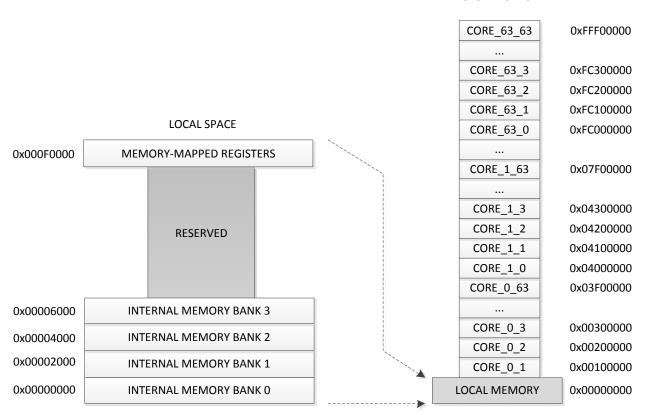

The Epiphany architecture uses a single, flat address space consisting of  $2^{32}$  8-bit bytes. Byte addresses are treated as unsigned numbers, running from 0 to  $2^{32} - 1$ . This address space is regarded as consisting of  $2^{30}$  32-bit words, each of whose addresses is word-aligned, which means that the address is divisible by 4. The word whose word-aligned address is A consists of the four bytes with addresses A, A+1, A+2 and A+3. Each mesh node has a local, aliased, range of memory that is accessible by the mesh node itself starting at address 0x00007FFF. Each mesh node also has a globally addressable ID that allows communication with all other mesh nodes in the system. The mesh-node ID consists of 6 row-ID bits and 6 column-ID bits situated at the upper most-significant bits (MSBs) of the address space. The complete memory map for the 32 bit Epiphany architecture is shown in Figure 5.

#### Figure 5: Epiphany Global Address Map

GLOBAL SPACE

Data and code can be placed anywhere in the memory space or in external space, except for the memory-mapped register space and reserved space, but performance is optimized when the data and code are placed in separate local-memory banks.

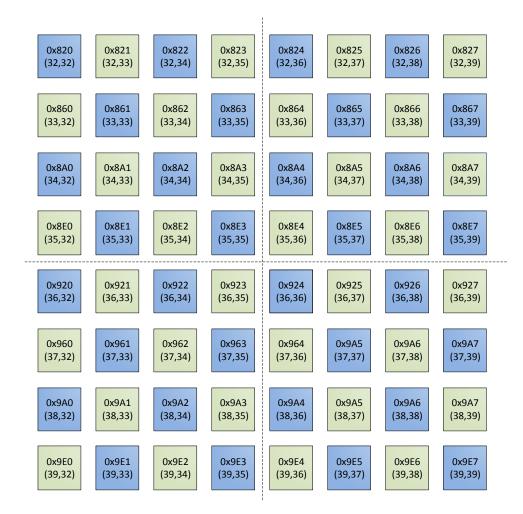

Figure 6 shows a 64-node region of the memory map, highlighting the upper address range of each mesh node and its corresponding mnemonic (row, column) coordinate. Note that the memory map laid out as a mesh to match the natural geometrical mapping of Epiphany's Network-On-Chip. The dotted line in Figure 6 shows the I/O boundary and memory map for a hypothetical system consisting of four 16-core chips connected in a glue-less fashion on a board. The 32-bit address map supports up to 4095 cores in a single shared memory system, but practically some of the memory space will probably be dedicated to off-chip SDRAM and memory mapped IO peripherals.

Figure 6: Epiphany Shared Memory Map

Each CPU can be accessed by any other CPU by specifying the appropriate row-column fields of the address in a memory read or write transactions. The startup cost for node-to-node communication is zero clock cycles. From a programmer's viewpoint, the only difference between on-chip communication and off-chip communication is in transaction bandwidth and latency. In the Figure 6 memory map, if core (32,32) wants to perform a read operation from core (39,39), it would send a read address with the upper bits 0x9e7 and specify a return address with upper bits 0x820 to the mesh network. The network takes care of the rest, making sure that the read request propagates to the read destination and that data is correctly returned to the mesh node that initiated the request.

#### 4.2 Memory Order Model

All read and write transactions from local memory follow a *strong memory-order model*. This means that the transactions complete in the same order in which they were dispatched by the program sequencer.

For read and write transactions that access non-local memory, the memory order restrictions are relaxed to improve performance. This is called a *weak memory-order model*. The following section explains the background of a weak memory-order model, how it is used by the Epiphany architecture, and how it affects determinism in the system. The relaxation of synchronization between memory-access instructions and their surrounding instructions is referred to as *weak ordering of loads and stores*. Weak ordering implies that the timing of the actual completion of the memory operations—even the order in which these events occur—may not align with how they appear in the sequence of the program source code. The only guarantees are:

- Load operations complete before the returned data is used by a subsequent instruction.

- Load operations using data previously written use the updated values.

- Store operations eventually propagate to their ultimate destination.

Weak ordering has some side-effects that programmers must be aware of in order to avoid improper system operation. When writing to or reading from non-local memory locations, such as off-chip I/O device registers and SDRAM, the order in which read and write operations complete is often significant, but is not guaranteed by the underlying hardware. To ensure that these effects do not occur in code that requires strong ordering of load and store operations, use run-time synchronization calls with order-dependent memory sequences.

Table **1** shows the ordering guaranteed in the Epiphany architecture. Instruction #1 refers to the first instruction in a sequential program, and instruction #2 refers to any instruction following the first one in that same program.

| First Transaction | Second Transaction | Deterministic Order |

|-------------------|--------------------|---------------------|

| Read from CoreX   | Read from CoreX    | Yes                 |

| Write to CoreX    | Write to CoreX     | Yes                 |

| Write to CoreX    | Read from CoreX    | No                  |

| Read from CoreX   | Write to CoreX     | Yes                 |

| Read from CoreX   | Read from CoreY    | Yes                 |

| Read from CoreX   | Write to CoreY     | Yes                 |

| Write to CoreX    | Write to CoreY     | No!                 |

| Write to CoreX    | Read from CoreY    | No!                 |

Table 1: Memory Transaction Ordering Rule

# 4.3 Endianness

The Epiphany architecture is a little-endian memory architecture. The figures below show how instructions and data are placed in memory with respect to byte order.

|    | Data In        | Register      |    |        | Data         | In Memory    |        |

|----|----------------|---------------|----|--------|--------------|--------------|--------|

| B3 | B2             | B1            | B0 | B3     | B2           | B1           | В0     |

|    |                |               |    | Addr+3 | Addr+2       | Addr+1       | Addr+0 |

| 32 | 2-Bit Instruct | ion In Regist | er |        | 32-Bit Instr | uction In Me | mory   |

| B3 | B2             | B1            | B0 | B3     | B2           | B1           | В0     |

|    |                |               |    | Addr+3 | Addr+2       | Addr+1       | Addr+0 |

| 16 | 6-Bit Instruct | ion In Regist | er |        | 16-Bit Instr | uction In Me | mory   |

| B1 | B0             | B1            | B0 | B1     | B0           | B1           | В0     |

|    |                |               |    | Addr+3 | Addr+2       | Addr+1       | Addr+0 |

# 4.4 Load/Store Alignment Restrictions

The Epiphany architecture expects all memory accesses to be suitably aligned: doubleword accesses must be doubleword-aligned, word accesses must be word-aligned, and halfword accesses must be halfword-aligned. Table 2 summarizes the restrictions on the three LSBs of the address used to access memory for each type of memory transaction. An "x" in the address field refers to a bit that can be any value. Load and store transactions with unaligned addresses generate a software exception that is handled by the node's interrupt controller. For unaligned write accesses, data is still written to memory, but the data written will be incorrect. Unaligned reads return values to the register file before an unaligned exception occur.

#### Table 2: Load and Store Memory-Alignment Restrictions

| Data Type  | Address[2:0] |

|------------|--------------|

| Byte       | Xxx          |

| Halfword   | xx0          |

| Word       | x00          |

| Doubleword | 000          |

# 4.5 Program-Fetch Alignment Restrictions

All instructions must be aligned on half-word boundaries.

# 5 eMesh Network-On-Chip

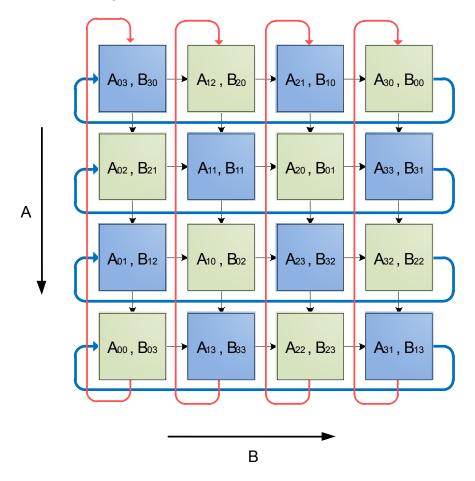

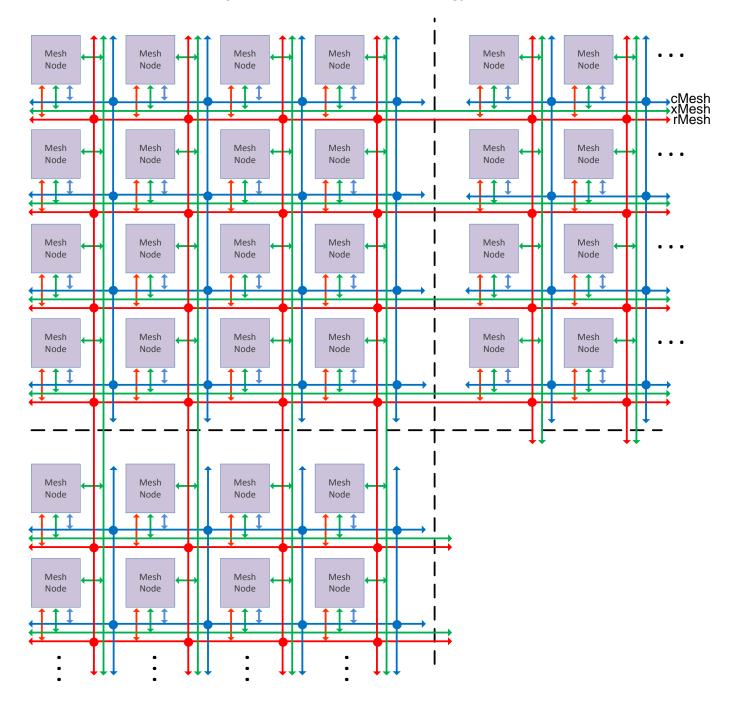

The eMesh Network-On-Chip is illustrated in Figure 2 and in Figure 7.

# 5.1 Network Topology

The eMesh network has a 2D mesh topology with only nearest-neighbor direct connections. Every router in the mesh is connected to the north, east, west, south, and to a mesh node. Write transactions move through the network, with a latency of 1.5 clock cycles per routing hop. A transaction traversing from the left edge to right edge of a 64- core chip would thus take 12 clock cycles. The edges of the 2D array can be connected to non-Epiphany interface modules, such as SRAM modules, FIFOs, I/O link ports, or standard buses such as AHB and AXI. Alternatively, the mesh edge connections can be left unconnected if not needed in the system.

The eMesh Network-on-Chip consists of three separate and orthogonal mesh structures, each serving different types of transaction traffic:

- *cMesh:* Used for write transactions destined for an on-chip mesh node. The cMesh network connects a mesh node to all four of its neighbors and has a maximum bidirectional throughput of 8 bytes/cycle in each of the four routing directions. At an operating frequency of 1GHz, the cMesh network has a total throughput of more than 0.5 Terabit/sec.

- *rMesh:* Used for all read requests. The rMesh network connects a mesh node to all four of its neighbors and has a maximum throughput of 1 read transaction every 8 clock cycles in each routing direction.

- *xMesh:* Used for write transactions destined for off-chip resources and for passing through transactions destined for another chip in a multi-chip system configuration. The xMesh network allows an array of chips to be connected in a mesh structure without glue logic. The xMesh network is split into a south-north network and an east-west network. The maximum throughput of the mesh depends on the available-off chip I/O bandwidth. Current silicon versions of the Epiphany architecture can sustain a total off-chip bandwidth of 8GB/sec.

Figure 7 shows a connection diagram of the three mesh networks. The example shows an Epiphany chip configuration with 16 mesh nodes per chip. Each mesh node is connected to all three mesh networks. The only difference between larger-array chips and smaller-array chips is in the divisor placement between the on-chip and off-chip transaction routing model. The off-chip boundary is indicated by a dotted line in the figure.

Figure 7: eMesh<sup>™</sup> Network Topology

The cMesh on-chip network has significantly lower latency and higher bandwidth than the xMesh network, so tasks with significant inter-task communication should be placed together on the same chip for optimal performance.

Key features of the eMesh network include:

- *Optimization of Write Transactions over Read Transactions*. Writes are approximately 16x more efficient than reads for on-chip transactions. Programs should use the high write-transaction bandwidth and minimize inter-node, on-chip read transactions.

- Separation of On-Chip and Off-Chip Traffic. The separation of the xMesh and cMesh networks decouples off-chip and on-chip communication, making it possible to write on-chip applications that have deterministic execution times regardless of the types of applications running on neighboring nodes.

- *Deadlock-Free Operation*. The separation of read and write meshes—together with a fixed routing scheme of moving transactions first along rows, then along columns—guarantees that the network is free of deadlocks for all traffic conditions.

- *Scalability*. The implementation of the eMesh network allows it to scale to very large arrays. The only limitation is the size of the address space. For example, a 32-bit Epiphany architecture allows for building shared memory systems with 4,096 processors and a 64-bit architecture allows for scaling up to 18 billion processing elements in a shared memory system.

# 5.2 Routing Protocol

The upper 12 bits of the destination address are used to route transactions to their destination. Along the way, these upper bits—6 bits for row and 6 bits for column—are compared to the rowcolumn ID of each mesh node in the routing path. Transactions are routed east if the destinationaddress column tag is less than the column ID of the current router node, and they are routed west if the destination-address column tag is greater than the column ID of the current router node.

Transactions first complete routing along a single row before traveling in a column direction. When the destination-address column tag matches the mesh-node column ID, a similar comparison is made in the row direction to determine whether the transaction should be routed to the south or to the north. The transaction routing continues until both the row tag and column tag for the destination match the row and column ID of the current mesh node. Then, the transaction is routed into the network interface of mesh node.

Table 3 summarizes the routing rules for the combinations of mesh-node IDs and transaction addresses.

| Address-Row Tag               | Address-Column Tag         | Routing Direction |

|-------------------------------|----------------------------|-------------------|

| Greater Than Mesh-Node Column | Don't Care                 | East              |

| Less Than Mesh-Node Column    | Don't Care                 | West              |

| Matches Mesh-Node Column      | Less Than Mesh-Node Row    | North             |

| Matches Mesh-Node Column      | Greater Than Mesh-Node Row | South             |

| Matches Mesh-Node Column      | Matches Mesh-Node Row      | Into Mesh Node    |

#### Table 3: Routing Protocol Summary

### 5.3 Read Transactions

Read transactions are non-blocking and are initiated as posted read requests to an address within the mesh fabric. A read request is sent out on the rMesh network and propagates towards the mesh node or external resource using the routing algorithm described in the previous section.

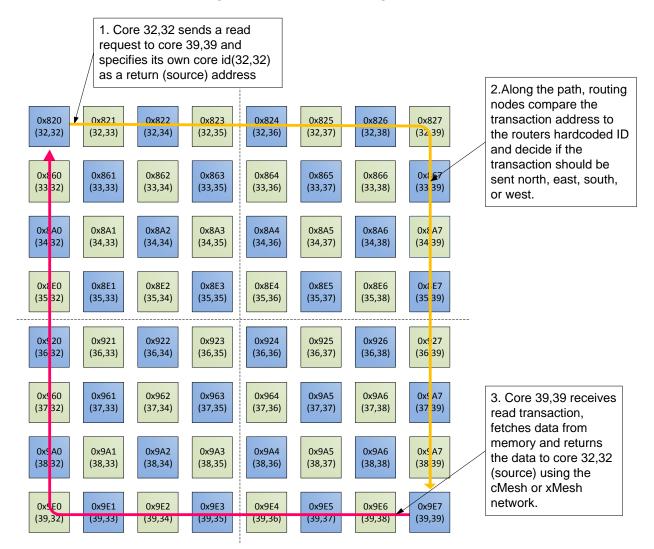

The source address is sent along with the read transaction on the outgoing read request. After the data has been read from the read address, the data is returned to the source address on the cMesh or xMesh network. The process is completely non-blocking, allowing transparent interleaving of read transactions from all mesh nodes. Figure 8 shows an example.

Figure 8: eMesh<sup>™</sup> Routing Example

# 5.4 Direct Inter-Core Communication

Figure 9 shows how the shared-memory architecture and the eMesh network work productively together. In the example, a dot-product routine writes its result to a memory location in another mesh node. The only thing required to pass data from one node to another is the setting of a pointer. The hardware decodes the transaction and determines whether it belongs to the local node's memory or to another node's memory. Since the on-chip cMesh network can accept write transactions at the same rate that a processor core can dispatch them, the example runs without pipeline stalls, despite executing a node-to-node write in the middle of the program stream. Using this method, programmers can reduce the cost of write-based inter-node communication to zero.

| C-CODE                                                                                      |               | ASSEMBLY                                                                                                              |

|---------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------|

| <pre>//VecA array at 0x82002000 //VecB array at 0x82004000 //remote_res at 0x92004000</pre> |               | <pre>//R0=pointer to VecA //R2=pointer to VecB //R6=pointer to remote_res //R4=loc_sum;</pre>                         |

| <pre>for (i=0; i&lt;100; i++) {   loc_sum+=vecA[i]*vecB[i]; } remote_res=loc_sum;</pre>     | $\rightarrow$ | MOV R5,#100;<br>_L: LDR R1,[R0],#1;<br>LDR R3,[R2],#1;<br>FMADD R4,R1,R3;<br>SUB R5,R5,#1;<br>BNE _L;<br>STR R4,[R6]; |

#### Figure 9: Pointer Manipulation Example

#### 5.5 Arbitration Scheme

The routers at every node in all three mesh networks contain round-robin arbiters. The arbitration hardware, in combination with the routing topologies, ensures that there are no deadlocks. The round-robin scheme also ensures that there is some split of available bandwidth between the competing agents on the network. The large on-chip bandwidth and non-blocking nature of the write network guarantees that no agent needs to wait more than a few clock cycles for access to the mesh. Applications requiring exact and deterministic bandwidth can implement network-resource interleaving in software.

### 5.6 Data Sizes and Alignment

The eMesh network supports byte, half-word, word, or double-word atomic transactions. Mesh data is always aligned to the least-significant bits (LSBs). Maximum bandwidth is obtained with double word transactions. All transactions should have addresses aligned according to the transaction data size.

#### 5.7 Multicast Routing

The eMesh supports efficient broadcasting of data to multiple cores through a special "multicast" routing mode. To use the multicast routing method, set the CTRLMODE field in the CONFIG register to 0011 in the master core sending eMesh write transactions. In multicast mode, the normal eMesh routing algorithm described in 5.2 is overridden and the transaction is instead routed radially outwards from the transmitting node. The write destination address is compared to the value found in the MULTICAST register at each eMesh node. If the eMesh write transaction address matches the MULTICAST register, the transaction enters the node.

#### 5.8 Detour Routing Support

The Epiphany-IV support modifying the eMesh routing at each node on a per mesh basis using the CMESHROUTE, XMESHROUTE, and RMESHSROUTE registers. Using these registers, it's possible to block or reroute transactions.

# 6 Processor Node Subsystem

### 6.1 Processor Node Overview

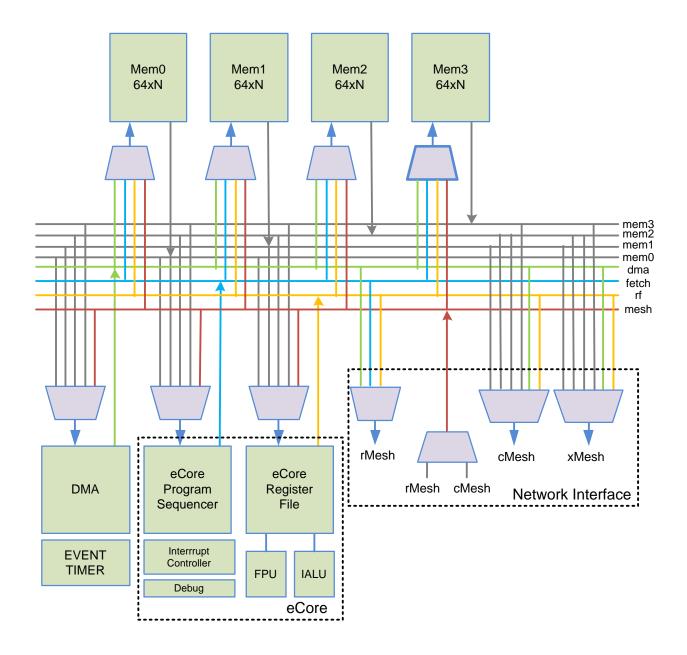

Figure 10 shows the components at each processor node, which include: an eCore RISC CPU, multi-bank local memory, multicore-optimized DMA engine, event monitor, and network interface. The node connects to the Epiphany eMesh network through the network interface, a single point of access.

#### Figure 10: Processor Node Overview

# eCore CPU

The heart of each processor node is the eCore CPU, a floating-point RISC microprocessor designed specifically for multicore processing and tuned to achieve a balance between performance, energy efficiency, and ease-of-use for many real-time applications. This balance of performance and data throughput makes performance levels close to 2 GFLOPS attainable in a large number of signal-processing kernels.

# **Local Memory**

A local memory system supports simultaneous instruction fetching, data fetching, and multicore communication. To accomplish this, the local memory is divided into four 8-byte-wide banks, each 8KB in size.

On every clock cycle, the following operations can occur:

- 64 bits of instructions can be fetched from memory to the program sequencer.

- 64 bits of data can be passed between the local memory and the CPU's register file.

- 64 bits can be written into the local memory from the network interface.

- 64 bits can be transferred from the local memory to the network using the local DMA.

In aggregate, the local memory supports 32 bytes of memory bandwidth per clock cycle, equivalent to 32 GB /sec at 1GHz. To maximize bandwidth, use doubleword transactions and place data and instructions so that two masters never access the same memory bank simultaneously.

# **Direct Memory Access (DMA) Engine**

The DMA engine accelerates data movement between processor nodes within the eMesh fabric. The engine was custom designed for the eMesh fabric and operates at the same speed as the eMesh, allowing it to generate a double word transaction on every clock cycle.

# **Event Timers**

Each processor node has two 32-bit event timers that can operate independently to monitor key events within the processor node. The timers can be used for program debug, program optimization, load balancing, traffic balancing, timeout counting, watchdog timing, system time, and numerous other purposes.

# **Network Interface**

The network interface connects all other parts of the processor node to the eMesh network-onchip. The network interface decodes load and store instructions, program counter addresses, and DMA-transaction addresses. It also decides whether a transaction is destined for the processor node itself (in which case bits [31:20] of the address are all zero) or for the mesh network. Arbitration is performed if more than one transaction is going out, in the same clock cycle, on one of the three network meshes. The network operates at the same frequency as the CPU and can output one transaction on the network per clock cycle. For double word write transactions, 8 bytes can be pushed onto the network on every clock cycle without stalling the pipeline.

# **Memory Protection Unit**

The memory protection unit provides the ability guard against unintended access of specific memory regions or cores.

# 6.2 Mesh-Node Crossbar Switch

The local memory in a processor node is split into 4 banks that are 8 bytes wide. The banks can be accessed in 1-byte transfers or in 8-byte transfers. All banks can be accessed once per clock cycle and operate at the same frequency as the CPU. The memory system in a single processor node thus supports 32GB/sec memory bandwidth at an operating frequency of 1 GHz.

Four masters can access the processor node local memory simultaneously:

- Instruction Fetch: This master fetches one 8-byte instruction from local memory into the instruction decoder of the program sequencer. The CPU's maximum instruction issue rate is two 32-bit instructions per clock cycle, so in heavily loaded program conditions, the program sequencer can access a memory bank on every clock cycle. The instruction-fetch logic can also fetch instructions directly from external memory or from other cores within the Epiphany fabric.

- Load/Store: This master copies data between the register file and a memory bank or external memory. Loads and stores can occur as 8-, 16-, 32-, or 64-bit transfers.

- **DMA:** Once set up, a DMA channel can work completely independently from the node's CPU to move data in and out of the node. Valid data-transfer sizes are 8, 16, 32, or 64 bits.

- **External**: An external agent may access the local memory to read or write certain address locations. Also, whenever the node initiates a read from an external memory location, the

transaction comes back as a write transaction that cannot be differentiated from an externally generated transaction.

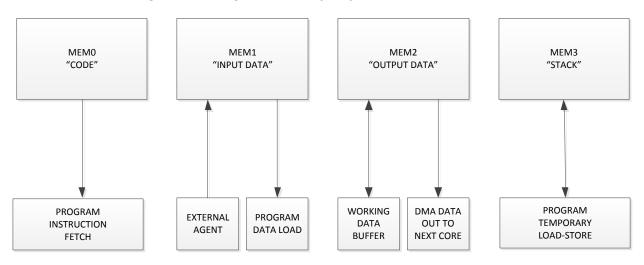

The figures below show examples of maximizing memory bandwidth by assigning data and code to memory banks within the 32 KB local memory. Figure 11 shows a program memory layout optimized for memory size.

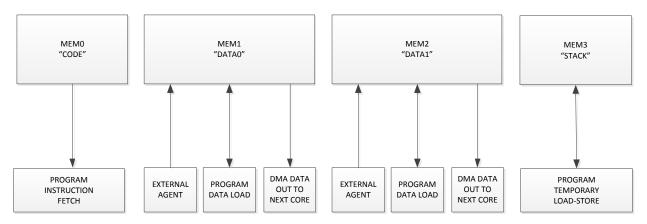

Figure 12 shows a program memory layout using a ping-pong configuration that is optimized for program speed.

Figure 11: Program Memory Layout Optimized for Size

Figure 12: Program Memory Layout Optimized for Speed

### 6.3 Mesh-Node Arbitration

The crossbar switch within a processor node implements fixed-priority arbitration. The arbiter is needed whenever there is a potential for a shared-resource conflict. Table 4 illustrates the access priority for the different masters within the processor node for different shared resources.

| Shared<br>Resource | Priority #1 | Priority #2   | Priority #3 | Priority #4   | Priority #5 |

|--------------------|-------------|---------------|-------------|---------------|-------------|

| Mem0               | cMesh       | rMesh         | Load-Store  | Program Fetch | DMA         |

| Mem1               | cMesh       | rMesh         | Load-Store  | Program Fetch | DMA         |

| Mem2               | cMesh       | rMesh         | Load-Store  | Program Fetch | DMA         |

| Mem3               | cMesh       | rMesh         | Load-Store  | Program Fetch | DMA         |

| rMesh              | Load-Store  | Program Fetch | DMA         | n/a           | n/a         |

| cMesh              | rMesh       | Load-Store    | DMA         | n/a           | n/a         |

| xMesh              | rMesh       | Load-Store    | DMA         | n/a           | n/a         |

| Register File      | cMesh       | rMesh         | Load-Store  | n/a           | n/a         |

#### **Table 4: Processor node Access Priorities**

# 7 eCore CPU

# 7.1 Overview

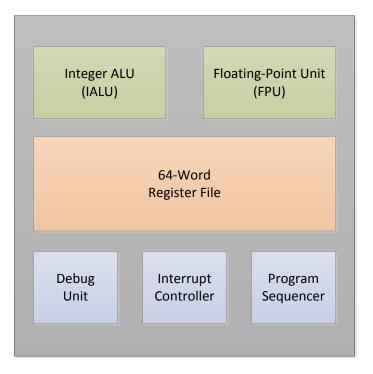

The different sub components of the eCore CPU are illustrated in Figure 13. The processor includes a general purpose program sequencer, large general purpose register file, integer ALU (IALU), floating point unit (FPU), debug unit, and interrupt controller.

### **Program Sequencer**

The program sequencer supports all standard program flows for a general-purpose CPU, including:

- *Loops*: One sequence of instructions is executed several times. Loops are implemented using general-purpose branching instructions, in which case the branching can be done by label or by register.

- *Functions*: The processor temporarily interrupts the sequential flow to execute instructions from another part of the program. The CPU supports all C-function calls, including recursive functions.

- *Jumps*: Program flow is permanently transferred to another part of the program. A jump by register instruction allows program flow to be transferred to any memory location in the 32-bit address space that contains valid program code.

- *Interrupts*: Interrupt servicing is handled by the interrupt controller, which redirects the program sequencer to an interrupt handler at a fixed address associated with the specific interrupt event. Before entering the interrupt service routine, the old value of the program counter is stored so that it can be retrieved later when the interrupt service routine finishes.

- *Idle*: A special instruction that puts the CPU into a low-power state waiting for an interrupt event to return the CPU to normal execution. This idle mode is useful, for example, in signal-processing applications that are real-time and data-driven.

- *Linear:* In linear program flows, the program sequencer continuously fetches instructions from memory to ensure that the processor pipeline is fed with a stream of instructions without stalling.

#### **Register File**

The 9-port 64-word register file provides operands for the IALU and FPU and serves as a temporary power-efficient storage place instead of memory. Arithmetic instructions have direct access to the register file but not to memory. Movement of data between memory and the register file is done through load and store instructions. Having a large number of registers allows more temporary variables to be kept in local storage, thus reducing the number of memory read and write operations. The flat register file allows user to balance resources between floating-point and integer ALU instructions as any one of the 64 registers be used by the floating-point unit or IALU, without restrictions.

In every cycle, the register file can simultaneously perform the following operations:

- Three 32-bit floating-point operands can be read and one 32-bit result written by FPU.

- Two 32-bit integer operands can be read and one 32-bit result written by IALU.

- A 64-bit doubleword can be written or read using a load/store instruction.

# Integer ALU

The Integer ALU (IALU) performs a single 32-bit integer operation per clock cycle. The operations that can be performed are: data load/store, addition, subtraction, logical shift,

arithmetic shift, and bitwise operations such as XOR and OR. The IALU's single-cycle execution means the compiler or programmer can schedule integer code without worrying about data-dependency stalls. All IALU operations can be performed in parallel with floating-point operations as long as there are no register-use conflicts between the two instructions. Pre- and post-modify addressing and doubleword load/store capability enables efficient loading and storing of large data arrays.

#### **Floating-Point Unit**

The floating-point unit (FPU) complies with the single precision floating point IEEE754 standard, executes one floating-point instruction per clock cycle, supports round-to-nearest even and round-to-zero rounding modes, and supports floating-point exception handling. The operations performed are: addition, subtraction, fused multiply-add, fused multiply-subtract, fixed-to-float conversion, absolute, float-to-fixed conversion.

Operands are read from the 64-entry register file and are written back to the register file at the end of the operation. No restrictions are placed on register usage. Regular floating-point operations such as floating-point multiply/add read two 32-bit registers and produce a 32-bit result. A fused multiply-add instruction takes three input operands and produces a single accumulated result. A large number of floating-point signal-processing algorithms use the multiply-accumulate operations, and for these applications the fused operations has the potential of reducing the number clock cycles significantly.

### **Interrupt Controller**

The interrupt controller supports up to 10 interrupts and exceptions, with full support for nested interrupts and interrupt masking.

#### **Hardware Loops**

Efficient zero overhead loops are supported through built in hardware support.

### **Debug Unit**

The debug unit provide multicore debug capabilities such as: single stepping, breakpoints, halt, and resume. For a complete description of supported debug features, please refer to the *Epiphany SDK Reference Manual*.

# 7.2 Data Types

The CPU architecture supports the following integer data types:

- Byte: 8 bits

- Half-Word: 16 bits (must be aligned on 2 byte boundary in memory)

- Word: 32 bits (must be aligned on 4 byte boundary in memory)

- Double: 64 bits (must be aligned on 8 byte boundary in memory)

The data types can be of signed or unsigned format, as shown below. All register-register operations operate on word types only, but data can be stored in memory as any size. For example, an array of bytes can be stored in memory by an external host, read into the register file using the byte load instruction, operated on as 32-bit integers, and then can stored back into memory using the byte store instruction.

# Signed Integer Representation

| msb                                                                                                               | lsb             |

|-------------------------------------------------------------------------------------------------------------------|-----------------|

| $-a_{N-1}\cdot 2^{N-1} a_{N-2}\cdot 2^{N-2} a_{N-3}\cdot 2^{N-3} a_{N-4}\cdot 2^{N-4} a_{N-5}\cdot 2^{N-5} \dots$ | $a_0 \cdot 2^0$ |

# **Unsigned Integer Representation**

| msb                                                                                                                   | lsb             |

|-----------------------------------------------------------------------------------------------------------------------|-----------------|

| $a_{N-1} \cdot 2^{N-1} a_{N-2} \cdot 2^{N-2} a_{N-3} \cdot 2^{N-3} a_{N-4} \cdot 2^{N-4} a_{N-5} \cdot 2^{N-5} \dots$ | $a_0 \cdot 2^0$ |

# **Floating-Point Data Types**

The FPU supports the IEEE754 32-bit single-precision floating-point data format, shown below:

| SIGN | EXP[7:0] | MANTISSA[22:0] |

|------|----------|----------------|

|------|----------|----------------|

A number in this floating-point format consists of a sign bit, s, a 24-bit mantissa, and an 8-bit unsigned-magnitude exponent, e. For normalized numbers, the mantissa consists of a 23-bit fraction, f, and a hidden bit of 1 that is implicitly presumed to precede f22 in the mantissa. The binary point is presumed to lie between this hidden bit and f22. The least-significant bit (LSB) of the fraction is f0; the LSB of the exponent is e0. The hidden bit effectively increases the

precision of the floating-point mantissa to 24 bits from the 23 bits actually stored in the data format. This bit also ensures that the mantissa of any number in the IEEE normalized number format is always greater than or equal to 1 and less than 2. The exponent, e, can range between  $1 \le e \le 254$  for normal numbers in the single-precision format. This exponent is biased by +127 (254/2). To calculate the true unbiased exponent, 127 must be subtracted from e.

The IEEE standard also provides for several special data types in the single-precision floatingpoint format, including:

- An exponent value of 255 (all ones) with a nonzero fraction is a not-a-number (NAN). NANs are usually used as flags for data flow control, for the values of uninitialized variables, and for the results of invalid operations such as 0 \* ∞.

- Infinity is represented as an exponent of 255 and a zero fraction. Because the number is signed, both positive and negative infinity can be represented.

- Zero is represented by a zero exponent and a zero fraction. As with infinity, both positive zero and negative zero can be represented. The IEEE single-precision floating-point data types supported by the processor and their interpretations are summarized in Table 5.

| Туре     | Sign | Exponent     | Mantissa | Value                                                          |

|----------|------|--------------|----------|----------------------------------------------------------------|

| NAN      | X    | 255          | Nonzero  | Undefined                                                      |

| Infinity | S    | 255          | Zero     | (-1) <sup>S</sup> * Infinity                                   |

| Normal   | S    | 1 <= e <=254 | Any      | $(-1)^{\mathrm{S}} * (1.\mathrm{M}_{22-0}) 2^{\mathrm{e}-127}$ |

| Denormal | S    | 0            | Any      | $(-1)^{\mathrm{S}} * \operatorname{Zero}$                      |

| Zero     | S    | 0            | 0        | $(-1)^{\mathrm{S}} * \mathrm{Zero}$                            |

### Table 5: IEEE Single-Precision Floating-Point Data Types

The CPU is compatible with the IEEE-754 single-precision format, with the following exceptions:

- No support for inexact flags.

- NAN inputs generate an invalid exception and return a quiet NAN. When one or both of the inputs are NANs, the sign bit of the operation is set as an XOR of the signs of the input sign bits.

- Denormal operands are flushed to zero when input to a computation unit and do not generate an underflow exception. Any denormal or underflow result from an arithmetic operation is flushed to zero and an underflow exception is generated.

- Round-to-±infinity is not supported.

By default, the FPU performs round-to-nearest even IEEE754 floating-point rounding. In this rounding mode, the intermediate result is rounded to the nearest complete number that fits within the final 32-bit floating-point data format. If the result before rounding is exactly halfway between two numbers in the destination format (differing by an LSB), the rounded result is that number which has an LSB equal to zero. Statistically, rounding up occurs as often as rounding down, so there is no large sample bias.

The FPU supports truncation rounding when the rounding mode bit is set in the Core Configuration Register. In truncate rounding mode, the intermediate mantissa result bits that are not within the first 23 bits are ignored. Over a large number of accumulations, there can be a large sample bias in the computation, so truncation rounding mode should be avoided for most applications.

The FPU detects overflow, underflow, and invalid conditions during computations. If one of these conditions is detected, a software exception signal is sent to the interrupt controller to start an exception handling routine.

Double-precision floating-point arithmetic is emulated using software libraries and should be avoided if performance considerations outweigh the need for additional precision.

# 7.3 Local Memory Map

Table 6 summarizes the memory map of the eCore CPU local memory.

| Name                       | Start Address | End Address | Size<br>(Bytes) | Comment                                 |

|----------------------------|---------------|-------------|-----------------|-----------------------------------------|

| Interrupt Vector<br>Table  | 0x00          | 0x3F        | 64              | Local Memory                            |

| Bank 0                     | 0x40          | 0x1FFF      | 8KB-64          | Local Memory Bank                       |

| Bank 1                     | 0x2000        | 0x3FFF      | 8KB             | Local Memory Bank                       |

| Bank 2                     | 0x4000        | 0x5FFF      | 8KB             | Local Memory Bank                       |

| Bank 3                     | 0x6000        | 0x7FFF      | 8KB             | Local Memory Bank                       |

| Reserved                   | 0x8000        | 0xEFFFF     | n/a             | Reserved for future<br>memory expansion |

| Memory Mapped<br>Registers | 0xF0000       | 0xF07FF     | 2048            | Memory mapped<br>register access        |

| Reserved                   | 0xF0800       | 0xFFFFF     | n/a             | N/A                                     |

### Table 6: eCore Local Memory Map Summary

All registers are memory-mapped and can be accessed by external agents through a read or write of the memory address mapped to that register or through a program executing MOVTS/MOVFS instructions. A complete listing of all registers and their corresponding addresses can be found in Appendix B. The eCore complete local memory space is accessible by any master within an Epiphany system by adding 12-bit processor node ID offset to the local address locations. Reading directly from the general-purpose registers by an external agent is not supported while the CPU is active. Unmapped bits and reserved bits within defined memory-mapped registers should be written with zeros if not otherwise specified.

# 7.4 General Purpose Registers

The CPU has a general-purpose register file containing 64 registers shown in Table 7. Generalpurpose registers have no restrictions on usage and can be used by all instructions in the Epiphany instruction-set architecture. The only general purpose register written implicitly by an instruction is register R14, used to save a PC on a functional call. The register convention shown in Table 9 shows the register usage assumed by the compiler to ensure safe design and interoperability between different libraries written in C and or assembly. The registers do not have default values.

| Name | Synonym | Role in the Procedure Call Standard              | Saved By     |

|------|---------|--------------------------------------------------|--------------|

| R0   | A1      | Argument/result/scratch register #1 Caller saved |              |

| R1   | A2      | Argument/result/scratch register #2              | Caller saved |

| R2   | A3      | Argument/result/scratch register #3              | Caller saved |

| R3   | A4      | Argument/result/scratch register #4              | Caller saved |

| R4   | V1      | Register variable #1                             | Callee Saved |

| R5   | V2      | Register variable #2                             | Callee Saved |

| R6   | V3      | Register variable #3                             | Callee Saved |

| R7   | V4      | Register variable #4   Callee Saved              |              |

| R8   | V5      | Register variable #5                             | Callee Saved |

| R9   | V6/SB   | Register variable #6/Static base                 | Callee Saved |

| R10  | V7/SL   | Register Variable #7/Stack limit                 | Callee Saved |

| R11  | V8/FP   | Variable Register #8/Frame Pointer               | Callee Saved |

| R12  | -       | Intra-procedure call scratch register            | Caller saved |

#### Table 7: General-Purpose Registers

| R13     | SP | Stack Pointer              | N/A          |

|---------|----|----------------------------|--------------|

| R14     | LR | Link Register              | Callee Saved |

| R15     |    | General Use                | Callee Saved |

| R16-R27 |    | General use                | Caller saved |

| R28-R31 |    | Reserved for constants N/A |              |

| R32-R43 |    | General use                | Callee saved |

| R44-R63 |    | General Use                | Caller saved |

The first four registers, R0-R3 (or A1-A4), are used to pass arguments into a subroutine and to return a result from a function. They can also be used to hold intermediate values within a function.

The registers R4-R8, R10, R11 (or V1-V5, V7-V8) are used to hold the values of a routine's local variables. The following registers are set implicitly by certain instructions and architecture convention dictates that they have fixed use. For more information regarding register usage, please refer to the Epiphany SDK reference manual.

- Stack Pointer: Register R13 is a dedicated as a stack pointer (SP).

- Link Register: The link register, LR (or R14), is automatically written by the CPU when the BL or JALR instruction is used. The register is automatically read by the CPU when the RTS instruction is used. After the linked register has been saved onto the stack, the register can be used as a temporary storage register.

# 7.5 Status Flags

The Core Status Register flags updated by the different instructions include:

# ACTIVE

When set, it indicates that core is currently active. The core is inactive at reset and is activated by an external agent asserting an interrupt. Once activated, the core stays active until the user asserts the IDLE instruction, at which time the core enters a standby state. During the standby state, core clocks are disabled and the power consumption is minimized. Applications that need minimal power consumption should use the IDLE instruction to put the core in a standby state and use interrupts to activate the core when needed.

# GID

When set it indicates that all external interrupts are blocked. The bit is set immediately on an interrupt occurring, giving the interrupt service routine enough time to save critical registers before another higher priority interrupt can occur. The flag is cleared by executing an RTI instruction, indicating the end of the service routine or by a GIE instruction indicating it is safe to allow a higher priority to begin if one is currently latched in the ILAT register.

### WAND

A multicore flag set by the WAND instruction. The WAND flag is an output of the core that gets "ANDed" together with the WAND flags from other cores to produce a global WAND interrupt when cores have raised their respective flags.

### AZ

The AZ (integer zero) flag set by an integer instruction when all bits of the result are zero and cleared for all other bit patterns. The flag is unaffected by all non-integer instructions.

### AN

The AN (integer negative) flag set to on by an integer instruction when the most-significant bit (MSB) of the result is 1 and cleared when the MSB of the result is 0. The flag is unaffected by all non-integer instructions.

AC

The AC (integer carry) flag is the carry out of an ADD or SUB instruction, is cleared by all other integer instructions, and is unaffected by all non-integer instructions.

### AV

The AV (integer overflow) flag set by the ADD instruction when the input signs are the same and the output sign is different from the input sign or by the SUB instruction when the second operand sign is different from the first operand and the resulting sign is different from the first operand. The flag is cleared by all other integer instructions and is unaffected by all non-integer instructions.

### BZ

The BZ (floating-point zero) flag is set by a floating-point instruction when the result is zero. The flag unaffected by all non-floating-point instructions.

### BN

The BN (floating-point negative) flag is set by a floating-point instruction when the sign bit (MSB) of the result is set to 1. The flag unaffected by all non-floating-point instructions.

### BV

The BV (floating-point overflow) flag is set by a floating-point instruction when the post rounded result overflows(unbiased exponent>127), otherwise the BV flag is cleared. The flag unaffected by all non-floating-point instructions.

### AVS

Sticky integer overflow flag set when the AV flag goes high, otherwise not cleared. The flag is only affected by the ADD and SUB instructions.

### BVS

Sticky floating-point overflow flag set when the BV flag goes high, otherwise not cleared. The flag is unaffected by all non-floating-point instructions.

### BIS

Sticky floating-point invalid flag set by a floating-point instruction if the either of the input operand is NAN, otherwise not cleared. The flag is unaffected by all non-floating-point instructions.

## BUS

Sticky floating-point underflow flag set by a floating-point instruction if the result is denormal or one of the inputs to the operation is denormal, otherwise not cleared. The flag is unaffected by all non-floating-point instructions.

# EXCAUSE

A three bit field indicating the cause of a software exception. A software exception edge interrupt is generated whenever this field is non-zero. The software exception cause values differ for Epiphany-III and IV and can be found in Appendix-C.

# 7.6 The Epiphany Instruction Set

The Epiphany instruction-set architecture (ISA) is optimized for real-time signal processing application, but it has all the features needed to also perform well in standard control code. Instruction-set highlights include:

- Orthogonal instruction set, with no restrictions on register usage.

- Instruction set optimized for floating point computation and efficient data movement.

- Post-modify load/store instructions for efficient handling of large array structures.

- Rich set of branch conditions, with 3-cycle branch penalty on all taken branches and zero penalty on untaken branches.

- Conditional move instructions to reduce branch penalty for simple control-code structures.

- Instructions with immediate modifies for high code density and low power consumption.

- Compact and efficient floating-point instruction set.

The ISA uses a split-width instruction encoding method, which improves code density compared with standard 32-bit width encoding. All instructions are available as both 16- and 32-bit instructions, with the instruction width depending on the registers used in the operation. Any command that uses registers 0 through 7 only and does not have a large immediate constant is encoded as a 16-bit instruction. Commands that use higher-numbered registers are encoded as 32-bit instructions. This encoding is transparent to the user, but is carefully integrated with the compiler to minimize C-based code size and power consumption.

The following section summarizes the instructions available in the Epiphany ISA. A complete alphabetical listing of the ISA can be found in Appendix A.

### **Branch Instructions**

Unrestricted branching is supported throughout the 32-bit memory map using branch instructions and register jump instructions. Branching can occur conditionally, based on the arithmetic flags set by the integer or floating-point execution unit. The following table illustrates the condition codes supported by the ISA. The architecture supports two sets of flags to allow independent conditional execution and branching of instructions based on results from two separate arithmetic units. The full set of branching conditions allows the synthesis of any high-level control comparison, including: <, <=, =, ==, !=, >=, and >. Both signed and unsigned arithmetic is supported.

| Code | Function                            | Mnemonic | Comment              |

|------|-------------------------------------|----------|----------------------|

| 0000 | Equal                               | BEQ      | AZ                   |

| 0001 | Not Equal                           | BNE      | ~AZ                  |

| 0010 | Greater Than (Unsigned)             | BGTU     | ~AZ & AC             |

| 0011 | Greater Than or Equal<br>(Unsigned) | BGTEU    | AC                   |

| 0100 | Less Than or Equal<br>(Unsigned)    | BLTEU    | AZ   ~AC             |

| 0101 | Less Than (Unsigned)                | BLTU     | ~AC                  |

| 0110 | Greater Than (Signed)               | BGT      | ~AZ & (AV ==AN)      |

| 0111 | Greater Than or Equal<br>(Signed)   | BGTE     | AV == AN             |

| 1000 | Less Than (Signed)                  | BLT      | AV !=AN              |

| 1001 | Less Than or Equal<br>(Signed)      | BLTE     | $AZ \mid (AV != AN)$ |

| 1010 | Equal (Float)                       | BBEQ     | BZ                   |

| 1011 | Not Equal (Float)                   | BBNE     | ~BZ                  |

| 1100 | Less Than (Float)                   | BBLT     | BN & ~BZ             |

| 1101 | Less Than or Equal (Float)          | BBLTE    | BN   BZ              |

| 1110 | Unconditional Branch                | В        | -                    |

| 1111 | Branch and Link                     | BL       | -                    |

# Table 8: Condition Codes

### Load/Store Instructions

Load and store instructions move data between the general-purpose register file and any legal memory location within the architecture, including external memory and any other eCore CPU in the system. All other instructions, such as floating-point and integer arithmetic instructions, are restricted to using registers as source and destination operands.

The ISA supports the following addressing modes:

- **Displacement Addressing:** The memory address is calculated by adding an immediate offset to a base register value. The immediate offset is limited to 3 bits for 16-bit load/store instructions or 11 bits for 32-bit load/store instructions. The base register value is not modified by the load/store operation. This mode is useful for accessing local variables.

- **Indexed Addressing:** The memory address is calculated by adding a register value offset to a base register value. The base register value is not modified by the load/store operation. This mode is useful in array addressing.

- **Post-Modify Auto-increment Addressing:** The memory address is taken directly from the base register value. After the memory operation has completed, a register offset is added to the base register value and written back to the base register. This mode is useful for processing large data arrays and for implementing an efficient stack-pop operation.

Byte, short, word, and double data types are supported by all load/store instruction formats. All loads and stores must be aligned with respect to the data size being used. Short (16-bit) data types must be aligned on 16-bit boundaries in memory, word (32-bit) data types must be aligned on 32-bit boundaries, and double (64-bit) data types must be aligned on 64-bit boundaries. Unaligned memory accesses returns unexpected data and generates a software exception. Double data-type load/store instructions must specify an even register in the general-purpose register file. The corresponding odd register is written implicitly. Attempts to use odd registers with double data format is flagged as an error by the assembler.

### **Integer Instructions**

General-purpose integer instructions, such as ADD, SUB, ORR, AND, are useful for control code and integer math. These instructions work with immediate as well as register-based operands. The instructions update the integer status bits of the STATUS register.

### **Floating-Point Instructions**

An orthogonal set of IEEE754-compliant floating-point instructions for signal processing applications. These instructions update the floating-point status bits of the STATUS register.

### **Secondary Signed Integer Instructions**

The basic floating point instruction set can be substituted with a set of signed integer instructions by setting the appropriate mode bits in the CONFIG register [19:16]. These instructions use the same opcodes as the floating-point instructions and include: IADD, ISUB, IMUL, IMADD, IMSUB.

### **Register Move Instructions**

All register moves are done as complete word (32-bit) entities. Conditional move instructions support the same set of condition codes as the branch instructions specified in Table 12.

### **Program Flow Instructions**

A number of special instructions used by the run time environment to enable efficient interrupt handling, multicore programming, and program debug.

The following set of tables summarizes the instructions available in the ISA.

### Table 9: Instruction Set Syntax